ACROVIEW Programmer Supports Chip Programming of AdvanceClip‘s 32-bit fixed-point digital proce

Ongke Technology, the leader in the chip programming industry, recently released the latest programming software update and the list of newly supported chip models. Among them, the burning of AdvanceClip's 32-bit fixed-point digital processor ADP32F12A-150BG has been supported by Programming's general Programmer platform AP8000.

ADP32F12A-150BG is a high-performance 32-bit fixed-point digital processor with low power consumption and high performance. Built-in a variety of memories and rich peripherals, with a wide range of applications. It is used in industrial intelligent control, Internet of Things wireless access, variable frequency electric drive, general signal processing, and other fields.

Product characteristics

• High-performance CMOS process

– Primary frequency 150MHz (cycle 6.67ns)

– Low power design (1.8V core, 3.3V I/O voltage)

– Integrated 1.8V linear regulated power supply (LDO)

• Support JTAG online simulation

• High-performance 32-bit CPU

– Single cycle 32-bit x32bit multiply-accumulate (MAC) operation

– Single cycle 2 16bit x16bit multiply-accumulate (MAC) operations

– Harvard bus architecture

– Atomic operation

– Fast interrupt response and handling

– Unified register programming mode

– 4M linear program/data address

– Efficient programming with C/C++and assembly language

• Chip memory resources

– Flash memory: 128Kx16 bit flash memory (4 8Kx16 bit and 6 16Kx16 bit sectors)

– ROM: 128Kx16 bit ROM (Note: Version C, customized)

– 1Kx16 OTP ROM

– L0 and L1: 2 blocks 4Kx16bit independently addressed SARAM

– H0: 1 8Kx16 bit SARAM

– M0 and M1: 2 1Kx16bit independently addressed SARAM

• Boot ROM (4Kx16bit)

– Support software boot mode

– Standard arithmetic table

• External storage expansion interface

– More than 1Mx16 bit expandable space

– Programmable wait state

– Programmable read/write timing

– 3 independent chip selection signals

• Clock and system control

– Support dynamic phase-locked loop (PLL) frequency division coefficient adjustment

– On-chip oscillator

– Watchdog timer

• Three external interrupt interfaces

• Peripheral interrupt expansion block (PIE) supporting 45 peripheral interrupts

• Three 32-bit CPU timers

• 128-bit security key/lock

– Protect Flash/ROM/OTP and L0/L1 SARAM

– Prevent reverse cracking of firmware

• Motor control peripherals (PWM generation circuit)

– Event Manager 1 (EM1), Event Manager 2 (EM2)

– Including 2 16-bit timers, 3 numerical comparators, 3 capture units, and 1 orthogonal encoding circuit

• Serial port peripherals

– Serial peripheral interface (SPI)

– 2 serial communication interfaces (SCI), compatible with UART standard

– Enhanced Controller Area Network (eCAN) controller, integrated on-chip eCAN driver

– Multichannel buffered serial port (McBSP)

• 12 bit 16 channel analog-to-digital converter (ADC)

– 2x8 channel input multiplexer

– Two sample and hold circuits

– Single/synchronous conversion

– Fast conversion rate: 80ns/12.5MSPS

• 56 general-purpose I/O (GPIO) pins

• Advanced simulation capabilities

– Analysis and breakpoint functions

– Hardware-based real-time debugging

development tool

– ANSI C/C++compiler/assembly language/connector

– Support Code Composer Studio ™ IDE

– Supports DSP/BIOS ™

– JTAG emulator

• Low power consumption mode and power saving mode

– Support IDLE, STANDBY, and HALT modes

– Independent peripheral clock can be disabled

• Strong electrostatic discharge (ESD) protection capability

– ESD human body mode (HBM):+4000V/- 4000V

– ESD machine mode (MM):+400V/- 400V

– Latch-up trigger current: 400mA

• Packaging options

– BGA179 (with external memory interface)

– LQFP176 (with external memory interface)

– LQFP128 (no external memory interface)

• Product grade

– S: Industrial grade

– A: consumption grade

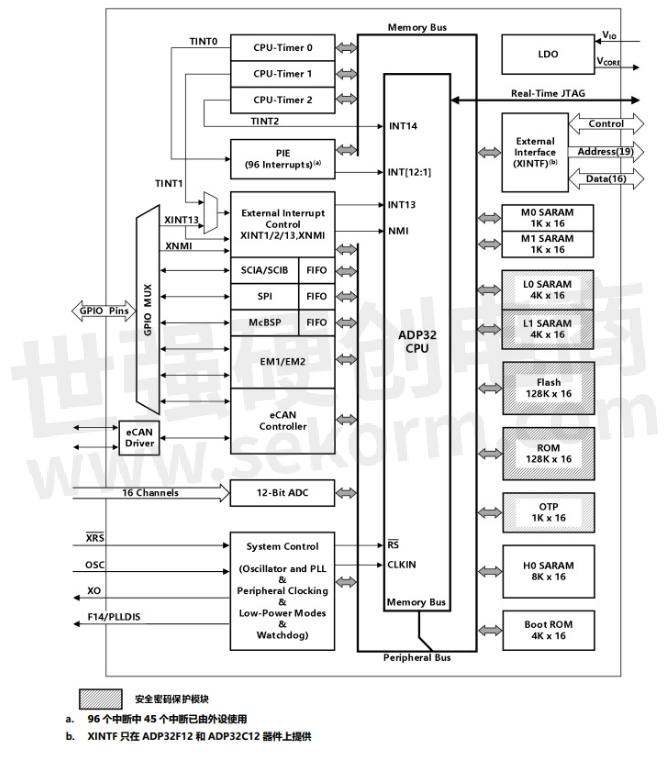

Functional block diagram

The AP8000 multi-purpose programmer independently developed by Acroview Technology(PTCHIP) consists of three parts: host, base plate, and adapter.

The host supports USB and NET connection, allowing multiple programmers to be networked, so as to control multiple IC programmers to burn at the same time. The built-in chip safety protection circuit ensures that even if the chip is put upside down or the short circuit is caused by other reasons can be detected immediately and power-off treatment can be carried out to ensure the safety of the chip and the programmer. Embedded high-speed FPGA, greatly accelerating data transmission and processing. There is an SD card slot on the back of the host computer. Put the project files made by PC software into the root directory of the SD card and insert them into the card slot. With the keys on the programmer, you can select, load, and execute commands such as burning the project files, so that you can operate without a PC, greatly reduce the cost of PC hardware configuration, and easily and quickly match the working environment.

The AP8000 makes the host more scalable by adding an adapter board to the backplane. At present, it has supported devices produced by all major semiconductor manufacturers, including TI, ST, Microchip, Atmel, Hynix, Macronix, Micron, Samsung, Toshiba, etc. Supported device types include NAND, NOR, MCU, CPLD, FPGA, EMMC, etc., and supported file formats include Intel Hex, Motorola S, Binary, POF, etc.

- +1 Like

- Add to Favorites

Recommend

- Acroview Programmer AP8000 Support the Programming of TI Texas Instruments Fuel Gauge BQ27500DRZR-V130

- At the time of setting sail, ACROVIEW Technology was awarded the recognition of Shenzhen‘s spec

- Universal Programmer AP8000 Supports Programming FuDanWei‘s Serial Flash Memory FM25Q16A

- Universal Programmer AP8000 Supports Programming TI‘s 32-Track PMBus Power Sequencer and System Manager UCD90320ZWSR

- Core Recording Micro‘s General Programming Platform AP8000 Support Programming TI‘s 32-bit Microcontroller TMS320F28066PZ

- Universal Programmer AP8000 Supports Programming of INGCHIPS‘ Low-power Bluetooth SoC Chip ING91880C

- Universal Programmer AP8000 Supports Programming TI‘s 32-bit Microcontroller TMS320F28377DPTPT

- Acroview Programmer AP8000 to Support the Programming of AdvanceChip‘s 32-bit Fixed-point Digital Signal Processor ADP32F035QP80S

This document is provided by Sekorm Platform for VIP exclusive service. The copyright is owned by Sekorm. Without authorization, any medias, websites or individual are not allowed to reprint. When authorizing the reprint, the link of www.sekorm.com must be indicated.