Dual, 16-bit, 125MSPS ADC CBM16AD125, Features A Multistage, Differential Pipelined Architecture

The CBM16AD125 is a dual, 16-bit, 125 MSPS analog-to-digital converter (ADC). The CBM16AD125 is designed to support communications applications where high performance, combined with low cost, small size, and versatility, is desired.

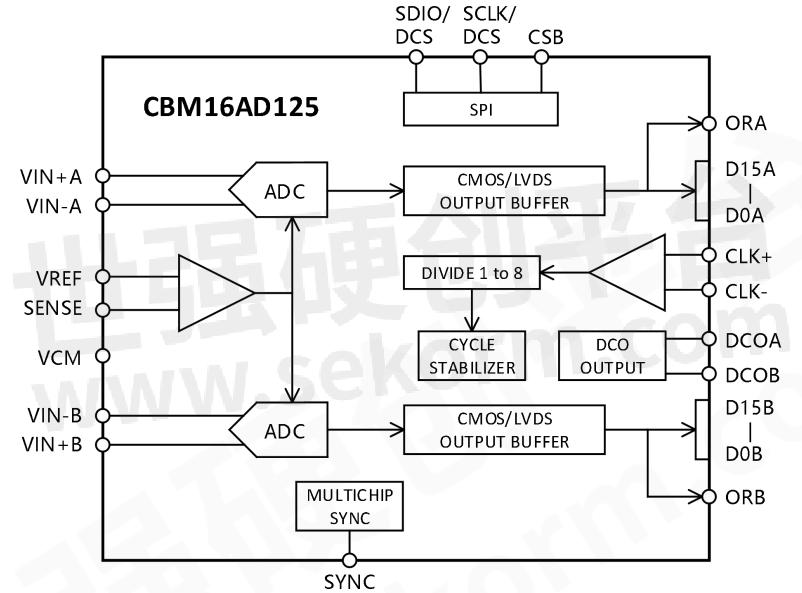

The dual ADC core features a multistage, differential pipelined architecture with integrated output error correction logic. Each ADC features wide bandwidth, and differential sample-and-hold analog input amplifiers that support a variety of user-selectable input ranges. An integrated voltage reference eases design consideration. A duty cycle stabilizer is provided to compensate for variations in the ADC clock duty cycle, allowing the converters to maintain excellent performance.

The ADC output data can be routed directly to the two external 16-bit output ports. These outputs can be set to either 1.8V CMOS or LVDS.

Flexible power-down options allow significant power savings when desired.

Programming for setup and control is accomplished using a 3-wire SPI-compatible serial interface.

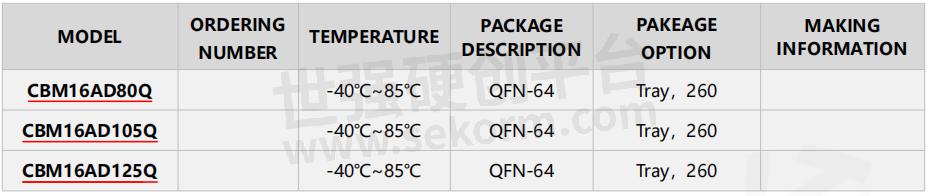

The CBM16AD125 is available in a 64-lead QFN and is specified over the industrial temperature range of −40℃ to +85℃.

Functional Block Diagram

Features

Low power: 800mW@125MSPS

Power supply:1.8V

CMOS or LVDS output supply: 1.8V

SNR=78dBFS (Fin=70MHz/Fs=125MSPS)

Spurious free dynamic range ( SFDR ): 88dBc (Fin=70MHz/Fs=125MSPS)

IF sampling frequencies to 300MHz

Integer 1-to-8 input clock divider

small-signal input noise: −153dBm/Hz (200Ω Input impedance / Fin=70MHz / Fs=125MSPS)

Programmable internal voltage reference

Differential analog input range: 2Vp-p (maximum)

Differential analog inputs bandwidth: 650MHz

ADC clock duty cycle stabilizer

95dB channel isolation/crosstalk

Serial port (SPI) control

User-configurable, built-in self-test (BIST) capability

Energy-saving power-down modes

Applications

Radar system

Diversity radio system

Multimode digital receivers (3G)

GSM/EDGE/W-CDMA/LTE/CDMA2000 WiMAX/TD-SCDMA

I/Q demodulation systems

Smart antenna systems

General-purpose software radios

Broadband data applications

Ultrasound equipment

Product Highlights

On-chip dither option for improved SFDR performance with low power analog input.

Proprietary differential input that maintains excellent SNR performance for input frequencies up to 300MHz.

Operation from a single 1.8V supply and a separate digital output driver supply accommodating 1.8V CMOS or LVDS outputs.

Standard serial port interface (SPI) that supports various product features and functions, such as data formatting (offset binary, twos complement, or gray coding), enabling the clock DCS, power-down, test modes, and voltage reference mode.

Pin compatibility with the AD9258/AD9268 allows a simple migration from 16 bits to 14 bits.

Package/Ordering Information

- +1 Like

- Add to Favorites

Recommend

- Corebai New Dual Comparator CBM2903 with Supply Range of +2V to +30V and Low Input Offset Voltage

- Corebai CBM317 Adjustable 3−terminal Positive Voltage Regulator Capable of Supplying in Excess of 1.5A over an Output Voltage Range of 1.2V to 37V

- A Real-time Clock IC with Two-wire Consecutive Interface

- CBM9001A Embedded USB Host Controller, Operating Full Speed at 12 Mbps with 256-byte Internal SRAM Buffer

- Bringing WIFI RF Front-end Chips, Low-noise Amplifiers, 5G Small Base Station RF Chips, CHIPBETTER Announced a Distribution with Sekorm

- CMOS Operational Amplifiers CBM8557/8/9 with Very Low Offset Voltage and Near-zero Drift Over Time and Temperature

- NOVOSENSE Has Launched Multiple Automobile-qualified Chips with Breakthrough Innovation Technology In the first half of 2022!

- Ruimeng 16/24 sigma-Delta ANALOG-to-digital converter won 2021 “Global Electronic Achievement Award“

This document is provided by Sekorm Platform for VIP exclusive service. The copyright is owned by Sekorm. Without authorization, any medias, websites or individual are not allowed to reprint. When authorizing the reprint, the link of www.sekorm.com must be indicated.