Empowering Innovation, Cologne Chip FPGA Solution: Ideal for Seamless Integration in Projects of Every Scale, from small to High-Volume Applications

The GateMateTM FPGA family of Cologne Chip AG addresses all application requirements of small to medium size FPGAs. Logic capacity, power consumption, package size, and PCB compatibility are best in class. GateMateTM FPGAs combine these features with the lowest cost in industry making the devices well-suited from University projects to high volume applications. Because of the outstanding circuit size/cost ratio, new applications now can use the benefits of FPGAs.

All this is based on a novel FPGA architecture combining CPE programmable elements with a smart routing engine. The CPE architecture allows an efficient building of arbitrarily-sized multipliers. Memory aware applications can use block RAMs with bit widths of 1 to 80 bits.

General Purpose IOs (GPIOs) can use different voltage levels from 1.2 to 2.5Volts. All GPIOs can be configured as single-ended or LVDS differential pairs. Furthermore, a high-speed SerDes interface is available.

FPGA designs are synthesized using the Yosys framework. The free Cologne Chip P&R-software generates the FPGA bitstream.

A Static Timing Analysis (STA) is also performed and gives evidence about critical paths and the overall performance of a design. The design can be simulated using Verilog netlist and SDF timing extraction.

The devices are manufactured using the GlobalfoundriesTM 28 nm SLP (Super Low Power) process. Due to manufacturing in Europe, there is no danger of trade restrictions or high taxation.

GateMateTM FPGA Overview

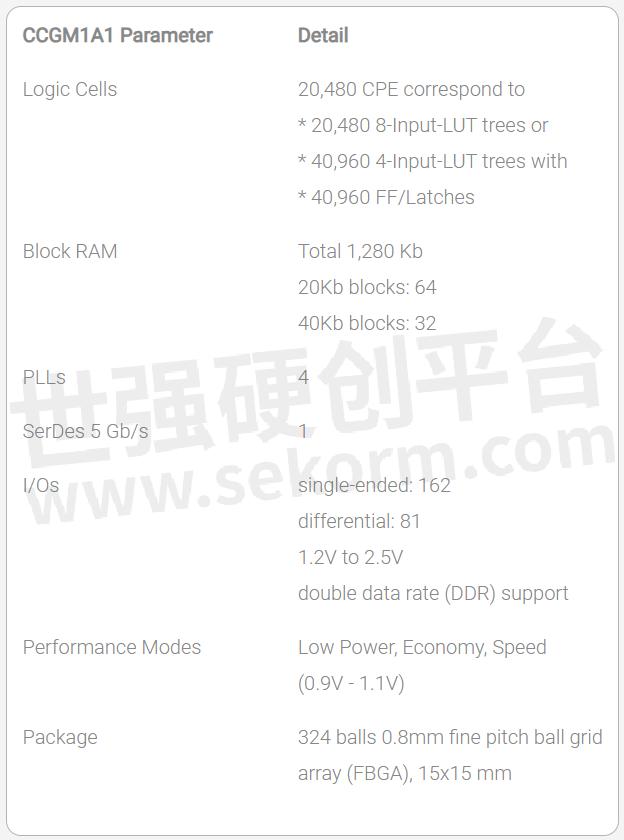

The GateMate A1 FPGA is the smallest-dimensioned component of the GateMateTM Series. With its 20,480 logic elements, it is ideally suited for lowest-power applications.

GateMateTM FPGA Features

Novel CPE Architecture

20,480 programmable elements (CPE) for combinatorial and sequential logic

40,960 Latches / Flip-Flops within programmable elements

CPE consists of LUT-tree with 8 inputs

Each CPE is configurable as a 2-bit full-adder or 2x2-bit multiplier

Low Power Consumption

GlobalfoundriesTM 28 nm SLP (Super Low Power) process

3 operation modes: low power, economy, speed

No excessive start-up currents

Only two supply voltages are needed and can be applied in any order

Features

4 programmable PLLs

Fast configuration with quad SPI interface up to 100 MHz

Multi-Chip configuration

1,280 Kbit dual ported block RAM with variable data widths in 32 x 40 Kbit RAM cells

Multipliers with arbitrary size implementable in CPE array

Multiple clocking schemas

All 162 GPIOs are configurable as single-ended or LVDS differential pairs

Double data rate (DDR) support in all GPIO cells

5 Gb/s SerDes

Package

324-ball BGA package (15x15mm)

Only 2 signal layers are required on the PCB

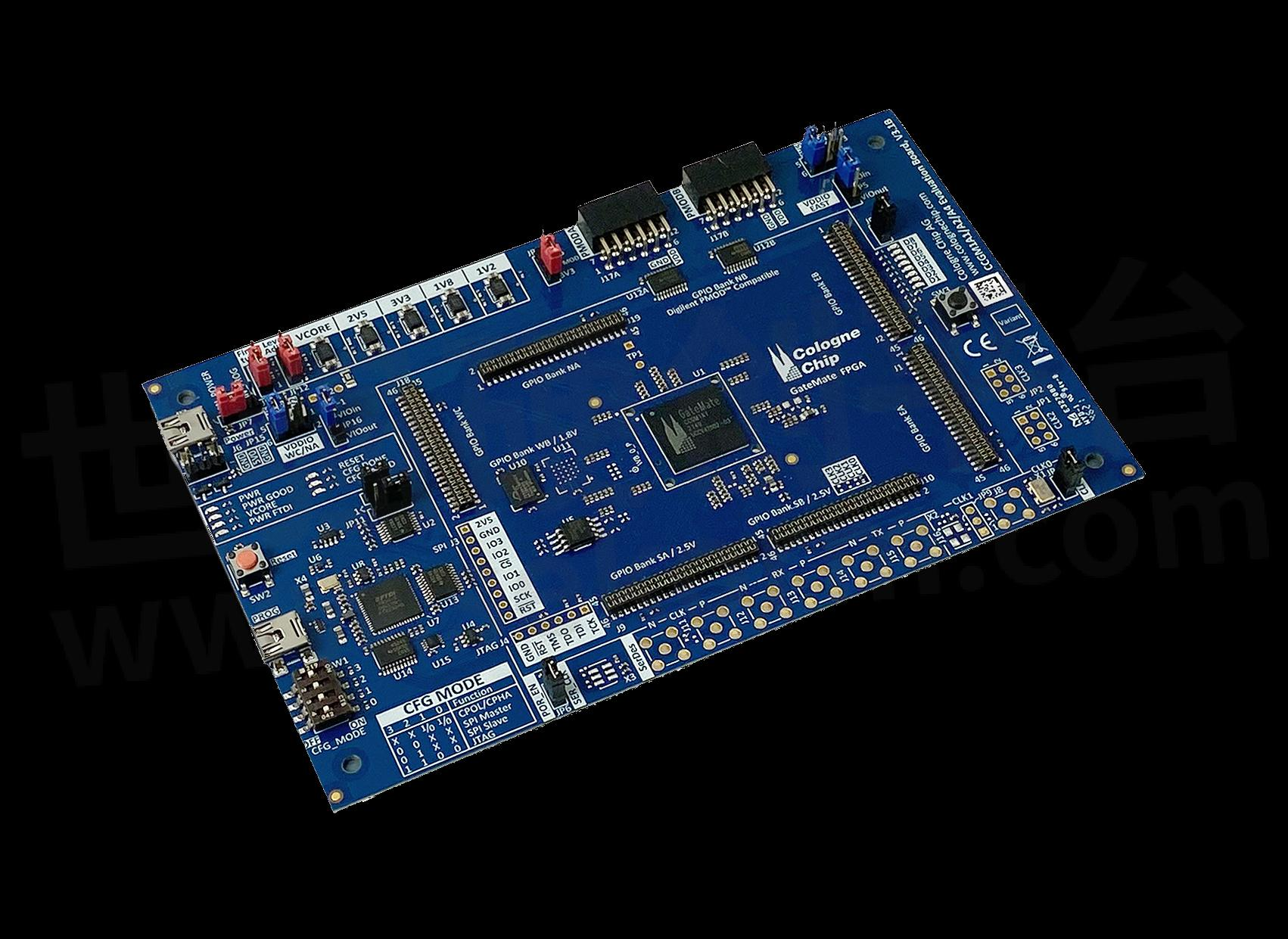

GateMateTM FPGA Starter Kit

The GateMateTM FPGA Starter Kit is the perfect starting point for all embedded designers exploring a flexible and low-power platform, based on the latest Cologne Chip technology and targeted at cost-sensitive designs.

The Starter Kit consists of all required hardware components for evaluating and developing a wide range of applications and includes:

Evaluation Board with GateMate A1 FPGA

Programmer Adapter and flat ribbon cable for your PCB

USB cable

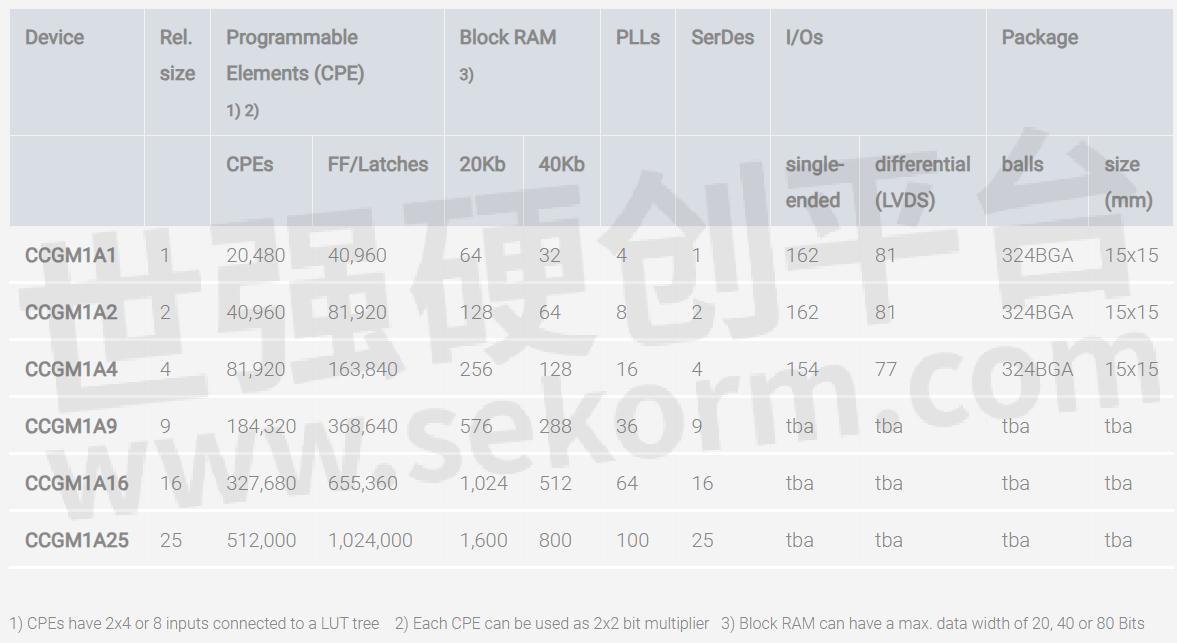

GateMateTM FPGA Series: Feature Summary by Device

The Cologne Chip GateMateTM family addresses a complete range of system requirements. The following table compares all available devices:

- +1 Like

- Add to Favorites

Recommend

- A powerful FPGA for a wide range of cost-effective solutions

- Summary of Chip Encapsulation Type-Is it Used with You?

- Dark tide in the shortage market: chip refurbishment

- The RS3005 Chip Developed by Runic Technology Helped The System MCU to Complete The Power Supply

- Bringing WIFI RF Front-end Chips, Low-noise Amplifiers, 5G Small Base Station RF Chips, CHIPBETTER Announced a Distribution with Sekorm

- 6 Bluetooth Beacons Based on nrf51822/nRF52832/nRF52810 Chip Solutions

- XBLW Chip Bo Le Analog Chip Series: Signal Chain Chips (Part 4)

- Focusing on design of security ASIC chip, NEOWINE provides anti-copy encryption chip, data security encryption chip, etc.

This document is provided by Sekorm Platform for VIP exclusive service. The copyright is owned by Sekorm. Without authorization, any medias, websites or individual are not allowed to reprint. When authorizing the reprint, the link of www.sekorm.com must be indicated.