Summary of Chip Encapsulation Type-Is it Used with You?

What do you know about chip packaging? Why should the chip be packaged? What are the chip types? Chip packaging: Simply speaking, the Die of integrated circuit produced by Foundry is put on a load-bearing substrate, then the pins are led out, and then fixed and packaged into a whole.

Fig.1

Chip packaging function: The chip plays the role of placing, fixing, sealing, protecting the chip and enhancing the electric heating performance, and it is also a bridge between the internal world of the chip and the external circuit-the contacts on the chip are connected to the pins of the package shell by wires, and these pins are connected with other devices by wires on the printed board. Therefore, packaging plays an important role in CPU and other LSI integrated circuits. There are too many types of chip packages in the world. Here, more than 70 common chip packages are summarized. I hope I can give you a general idea of packaging.

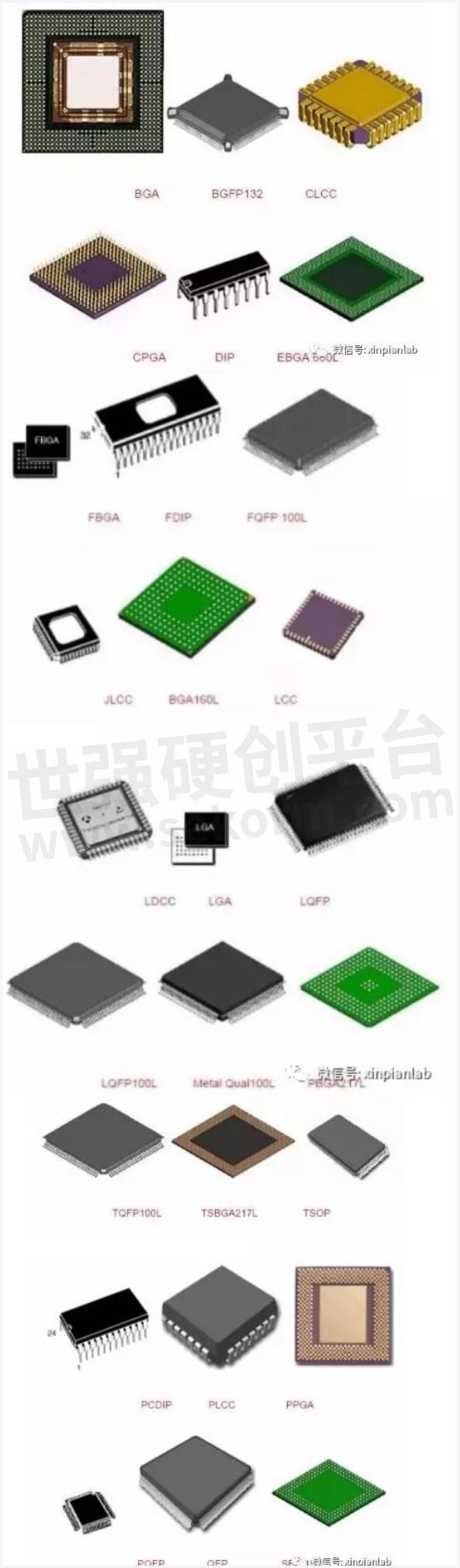

Fig.2

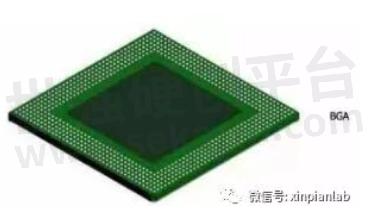

1、BGA(ball grid array) ball contact array, one of surface mount packages. On the back of the printed substrate, spherical bumps are made to replace pins, and LSI chips are assembled on the front of the printed substrate, and then sealed by molding resin or potting. Also known as the bump display carrier (PAC). The number of pins can exceed 200, which is a package for multi-pin LSI. The package body can also be made smaller than QFP (Four-sided Flat Package). For example, a 360-pin BGA with a pin center distance of 1.5mm is only 31mm square; While the 304-pin QFP with a pin center distance of 0.5mm is 40mm square. And BGA doesn't have to worry about pin deformation like QFP. This package was developed by Motorola Company of the United States. It was first used in portable phones and other devices, and may be popularized in personal computers in the United States in the future. At first, the center-to-center distance of the pins (bumps) of BGA was 1.5mm, and the number of pins was 225. Now some LSI manufacturers are developing 500-pin BGA. The problem of BGA is the appearance inspection after reflow soldering. It is not clear whether it is an effective appearance inspection method. Yes, because of the large distance between the centers of welding, the connection can be regarded as stable and can only be handled by functional inspection. Motorola Company of the United States calls the package sealed by molding resin OMPAC, while the package sealed by potting method is called GPAC (see OMPAC and GPAC).

Fig.3

2、BQFP(quad flat package with bumper) Four-sided lead flat package with cushion. As one of QFP packages, bumps (cushion pads) are arranged at four corners of the package body to prevent the pins from bending and deforming during transportation. Semiconductor manufacturers in the United States mainly use this package in microprocessor and ASIC circuits. Pin-to-pin distance is 0.635mm, and the number of pins ranges from 84 to 196 (see QFP).

Fig.4

3、Butt joint pin grid array is another name for surface mount PGA (see surface mount PGA).

Fig.5

4、C-(ceramic) indicates the mark of ceramic packaging. For example, CDIP stands for ceramic DIP. It is a sign that is often used in practice.

5、Cerdip is a ceramic dual in-line package sealed by glass, which is used in ECL RAM, DSP and other circuits. Cerdip with glass window is used for ultraviolet erasing EPROM and microcomputer circuit with EPROM inside. The pin center distance is 2.54mm, and the number of pins ranges from 8 to 42. In Japan, this package is denoted as DIP-G(G (G means glass sealing).

6. One of the Cerquad surface mount packages, that is, the ceramic QFP sealed under it is used to package logic LSI circuits such as DSP. Cerquad with windows is used to package EPROM circuits. The heat dissipation is better than that of plastic QFP, and the power of 1. 5 ~ 2W can be allowed under natural air cooling condition. But the packaging cost is 3 ~ 5 times higher than that of plastic QFP. The pin pitch is 1.27mm, 0.8mm, 0.65mm, 0.5mm, 0.4mm and other specifications. The number of pins is from 32 to 368.

7. CLCC (Ceramic Led Chip Carrier) is a ceramic chip carrier with pins, which is one of the surface mount packages. The pins are led out from the four sides of the package and are T-shaped. Windows are used to package ultraviolet erasable EPROM and microcomputer circuits with EPROM. This package is also called QFJ, QFJ-G (see QFJ).

Fig.6

8、Chip packaging on COB(chip on board) is one of the bare chip mounting technologies. Semiconductor chips are hand-over mounted on printed circuit boards, and the electrical connection between the chip and the substrate is realized by wire stitching. The electrical connection between the chip and the substrate is realized by wire stitching and covered with resin to ensure reliability. Although COB is the simplest bare chip mounting technology, its packaging density is far less than that of TAB and flip chip bonding technology.

9、DFP(dual flat package) two-sided lead flat package. Is another name for SOP (see SOP). It used to be called this term, but now it is not used.

10. nickname of DIC(dual in-line ceramic package) ceramic DIP (including glass seal) (see DIP).

11. nickname of DIL(dual in-line)DIP (see DIP). European semiconductor manufacturers often use this name.

12. DIP(dual in-line package) dual in-line package. One of the plug-in packages, the pins are led out from both sides of the package, and the packaging materials are plastic and ceramic. DIP is the most popular plug-in package, and its applications include standard logic IC, memory LSI, microcomputer circuits, etc. The pin spacing is 2.54mm, and the number of pins ranges from 6 to 64. Package width is usually 15.2mm .. Some packages with widths of 7.52mm and 10.16mm are called skinny DIP and slim DIP, respectively. But in most cases, there is no distinction, and it is simply called DIP. In addition, ceramic DIP sealed with low melting point glass is also called credip (see cerdip).

Fig.7

13、DSO(dual small out-lint) Two-sided Pin Small Form Factor Package. Another name for SOP (see SOP). Some semiconductor manufacturers adopt this name.

14、DICP(dual tape carrier package) double-sided lead loaded package. One of TCP (Load Encapsulation). The pins are made on the insulating tape and led out from both sides of the package. Due to the use of TAB (Automatic On-Load Soldering) technology, the package is very thin. Commonly used in liquid crystal display drive LSI, but most of them are fixed products. In addition, the thin package of 0.5mm thick memory LSI is in the development stage. In Japan, DICP is named DTP according to the standard of EIAJ (Japan Electronics Machinery Industry Association).

15. DIP(dual tape carrier package) is the same as above. Nomenclature of DTCP in Japan Electronic Machinery Industry Association Standard (see DTCP). 16. FP(flat package) flat package. One of the surface mount packages. Another name for QFP or SOP (see QFP and SOP). Some semiconductor manufacturers adopt this name.

17. flip-chip reverse welding chip. One of the bare chip packaging technologies is to make metal bumps on the electrode area of the LSI chip, and then bond the metal bumps with the electrode area on the printed substrate. The footprint of the package is the same as the chip size. It is the smallest and thinnest of all packaging techniques. However, if the thermal expansion coefficient of the substrate is different from that of the LSI chip, there will be a reaction at the joint, which will affect the reliability of the connection. Therefore, the resin must be used to reinforce LSI chips, and substrate materials with basically the same thermal expansion coefficient must be used.

18. FQFP(fine pitch quad flat package) small pin center distance QFP. Generally, the center distance of the guide pin is less than 0.65mm (see QFP). Some conductor manufacturers adopt this name.

19. CPAC(globe top pad array carrier) is another name for BGA (see BGA) of Motorola Company of the United States.

20. cqfp (quad fiat package with guard ring) is a four-sided flat package with a guard ring. In one of the plastic QFPs, the pins are covered with a resin protection ring to prevent bending and deformation. Before the LSI is assembled on the printed circuit board, cut the pins from the guard ring and make them gull wing (L-shaped). This kind of package has been mass-produced by Motorola Company in the United States. Pin-to-pin distance is 0.5mm, and the maximum number of pins is about 208.

21. H-(with heat sink) indicates the mark with the radiator. For example, HSOP stands for SOP with a heat sink.

Fig.8

22、Grid array (surface mount type) surface mount PGA. PGA is usually a plug-in package with a pin length of about 3.4mm. Surface mount PGA has display pins on the bottom of the package, and their lengths range from 1.5mm to 2.0 mm. It adopts the method of bump welding with printed substrate, so it is also called bump welding PGA. Because the pin center distance is only 1.27mm, which is half smaller than the plug-in PGA, the package body can be made small, and the number of pins is more than that of plug-in PGA (250 ~ 528), so it is a package for large-scale logic LSI. The packaging substrate has a multilayer ceramic substrate and glass epoxy resin printing base. Packaging made of multilayer ceramic substrate has been put into practice.

23、Jlcc (j-led chip carrier) J-shaped lead chip carrier. Refers to the nicknames of CLCC with windows and QFJ with windows (see CLCC and QFJ). The name was adopted by some semiconductor manufacturers.

Fig.9

24、Lcc (leaderless chip carrier) leadless chip carrier. It refers to the surface mount package with only electrodes on four sides of the ceramic substrate and no pins. It is a package for high-speed and high-frequency IC, also known as ceramic QFN or QFN-C (see QFN).

Fig.10

25LGA(land grid array) touch point display package. That is, a package with array-state flat electrode contacts is made on the bottom surface. When assembling, just plug in the socket. At present, ceramic LGA with 227 contacts (1.27mm center distance) and 447 contacts (2.54mm center distance) has been used in high-speed logic LSI circuits. Compared with QFP, LGA can accommodate more input and output pins in a smaller package. In addition, because the impedance of the lead is small, it is very suitable for high-speed LSI. However, due to the complicated manufacture and high cost of the socket, it is not used now. It is expected that the demand for it will increase in the future.

LOC (Lead on Chip) refers to a chip packaging technique where the lead frame is positioned above the chip, and electrical connections are made by bonding wires to solder bumps located near the center of the chip. This structure allows for a narrower width of the chip within the same size package compared to the traditional placement of the lead frame near the side of the chip.

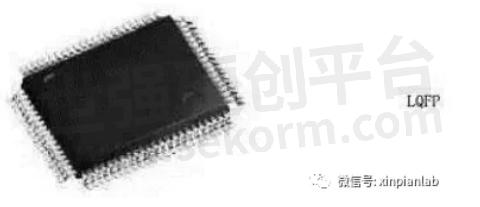

LQFP (Low Profile Quad Flat Package) is a type of QFP package with a thickness of 1.4mm. It is named according to the new QFP outline specifications established by the Japan Electronics and Machinery Industries Association.

Fig.11

28、One of L-Quad ceramic QFP. Aluminum nitride used for packaging substrate has 7 ~ 8 times higher thermal conductivity than aluminum oxide and has better heat dissipation. The packaging frame is made of alumina, and the chip is sealed by the potting method, thus suppressing the cost. It is a package developed for logic LSI, which can allow W3 power under natural air cooling conditions. At present, 208-pin (0.5mm center distance) and 160-pin (0.65mm center distance) LSI logic packages have been developed and put into mass production in October 1993.

29、MCM(multi-chip module) multi-chip module. A package in which a plurality of semiconductor bare chips are assembled on a wiring substrate. According to the substrate materials, it can be divided into three categories: MCM-L, MCM-C, and MCM-D. MCM-L is an assembly using a common glass epoxy resin multilayer printed substrate. The wiring density is not very high and the cost is low. MCM-C is an assembly with multilayer wiring formed by thick film technology and ceramic (alumina or glass ceramic) as substrate, similar to thick film hybrid IC with multilayer ceramic substrate. There is no obvious difference between the two. The wiring density is higher than MCM-L .. MCM-D is a multi-layer wiring formed by thin film technology, with ceramics (alumina or aluminum nitride) or Si and Al as the components of the substrate. Cabling is the highest among the three components, but the cost is also high.

30. MFP(mini flat package) is a small flat package. Another name for plastic SOP or SSOP (see SOP and SSOP). The name was adopted by some semiconductor manufacturers.

31. MQFP(metric quad flat package) is a classification of QFP according to JEDEC (United States Joint Electronic Equipment Committee) standard. Standard QFP (see QFP) with a center distance of 0.65mm and a thickness of 3.8mm~2.0mm.

32. MQUAD(metal quad) is a QFP package developed by Olin Company of America. And the base plate cover are made of aluminum and sealed with adhesive. The power of 2.5W~2.8W can be allowed under the condition of natural air cooling. Shin Kong Electric Industry Co., Ltd. of Japan was licensed to start production in 1993.

33. Another name for MSP(mini square package) is QFI (see QFI), which is often called MSP in the early stage of development. QFI is the name specified by the Japan Electronic Machinery Industry Association.

34. OPMAC (Overmolded Pad Array Carrier) molded resin-sealed bump display carrier. The name was adopted by Motorola Company of the United States for BGA sealed with molded resin (see BGA).

35. P-(plastic) indicates the mark of plastic packaging. For example, PDIP stands for plastic DIP.

36、PAC(pad array carrier), another name for BGA (see BGA).

37、Pclp (printed circuit board leaderless package) printed circuit board leaderless package. The name was adopted by Fujitsu Corporation of Japan for plastic QFN (plastic LCC) (see QFN). There are two specifications of pin pitch: 0.55mm and 0.4mm At present, it is in the development stage.

38、PFPF(plastic flat package) plastic flat package. Another name for plastic QFP (see QFP). The name was adopted by some LSI manufacturers.

39、PGA(pin grid array) pin package. One of the plug-in packages, in which the vertical pins on the bottom surface are arranged in an array. The package adopts multilayer ceramic substrates. Without the specific name of the material, most of them are ceramic PGA, which is used for high-speed large-scale logic LSI circuits. The cost is high. The pitch between pins is usually 2.54mm, and the number of pins ranges from 64 to 447. To reduce the cost, the packaging substrate can be replaced by a glass epoxy resin printed substrate. There are also plastic PG A with 64 ~ 256 pins. In addition, there is a short-pin surface mount PGA (bump-welded PGA) with a pin center distance of 1.27 mm. (see surface mount PGA).

40. piggyback piggyback package. Refers to the ceramic package with socket, and its shape is similar to DIP, QFP, and QFN. It is used to evaluate the program confirmation operation when developing the equipment with the microcomputer. For example, plug the EPROM into the socket for debugging. This kind of packaging is basically a fixed product, and it doesn't circulate in the market.

41. PLCC (Plastic Led Chip Carrier) Plastic chip carrier with leads. One of the surface mount packages. The pins are led out from the four sides of the package and are T-shaped. They are plastic products. Texas Instruments Company first adopted it in 64-bit DRAM and 256-bit RAM, and now it is widely used in logic LSI, DLD (or program logic device), and other circuits. The pin spacing is 1.27mm, and the number of pins ranges from 18 to 84. J-shaped pins are not easily deformed, which is easier to operate than QFP, but the appearance inspection after welding is more difficult. Plc is similar to LCC (also called QFN). In the past, the difference between the two is that the former uses plastic and the latter uses ceramic. But now, there are J-shaped lead packages made of ceramic and leadless packages made of plastic (labeled plastic LCC, PC LP, P-LCC, etc.), which can't be distinguished. For this reason, the Japan Electronic Machinery Industry Association decided in 1988 to call the package with J-shaped leads from four sides QFJ and the package with electrode bumps on four sides QFN (see QFJ and QFN).

42. P-LCC (Plastic Teadles Chip Carrier) (Plastic Led Chip Currier) is sometimes another name for plastic QFJ, and sometimes another name for QFN (Plastic LCC) (see QFJ and QFN). Some LSI manufacturers use P-LCC for lead packages and P-LCC for leadless packages to show the difference.

43. QFH(quad flat high package) is a thick flat package with four pins. A kind of plastic QFP. To prevent the package body from breaking, the QFP body is made thicker (see QFP). The name adopted by some semiconductor manufacturers.

44. QFI (Quad Flat I-led Pack GAC) is a flat package with four I-shaped pins. One of the surface mount packages. The pins are led out from the four sides of the package, and are I-shaped downwards. Also known as MSP (see MSP). Touch-and-weld connection with the printed substrate. Because the pins have no protruding parts, the mounting area is smaller than QFP. Hitachi has developed and used this package for video analog IC. In addition, Japan's Motorola PLL IC also adopts this package. The pin spacing is 1.27mm, and the number of pins is from 18 to 68.

45. QFJ (Quad Flat J-led Package) is a flat package with four J-shaped pins. One of the surface mount packages. The pins are led out from the four sides of the package and form a J-shape downward. It is the name specified by Japan Electronic Machinery Industry Association. Pin-to-pin spacing is 1.27mm. There are two kinds of materials: plastic and ceramic. In most cases, plastic QFJ is called PLCC (see PLCC) and is used for microcomputer, door display, DRAM, ASSP, OTP and other circuits. The number of pins is from 18 to 84. Ceramic QFJ is also called CLCC and JLCC (see CLCC). The package with window is used for ultraviolet erasing EPROM and microcomputer chip circuit with EPROM. The number of pins is from 32 to 84.

46. QFN (Quad Flat Non-led Package) is a flat package with no leads on four sides. One of the surface mount packages. Now it is called LCC. QFN is the name specified by Japan Electronic Machinery Industry Association. The four sides of the package are equipped with electrode contacts. Because there are no pins, the mounting area is smaller than QFP and the height is lower than QFP. However, when the stress is generated between the printed substrate and the package, it cannot be relieved at the electrode contact. Therefore, it is difficult to make as many electrode contacts as QFP pins, generally about 14 to 100. There are two kinds of materials: ceramic and plastic. When there is LCC mark, it is ceramic QFN. Electrode center distance is 1.27mm .. Plastic QFN is a low-cost package of glass epoxy resin printed substrate. In addition to 1.27mm, the center distance between the electrodes is 0.65mm and 0.5 mm. This kind of package is also called plastic LCC, PCLC, P-LCC, etc.

47、QFP(quad flat package) is a flat package with four leads. One of the surface mount packages, the pins are led out from four sides in a gull wing (L) shape. There are three kinds of base materials: ceramic, metal and plastic. In terms of quantity, plastic packaging accounts for the vast majority. When materials are not specifically indicated, most cases are plastic QFP. Plastic QFP is the most popular multi-pin LSI package. It is not only used in digital logic LSI circuits such as microprocessors and door displays, but also used in analog LSI circuits such as VTR signal processing and audio signal processing. Pin-to-pin spacing is 1.0mm, 0.8mm, 0.65mm, 0.5mm, 0.4mm, 0.3mm and other specifications. The maximum number of pins in the 0.65mm center distance specification is 304. The QFP whose pin center distance is less than 0.65mm is called QFP(FP). Now, however, Japan Electronic Machinery Industry Association has re-evaluated the external specifications of QFP. There is no difference in pin center distance, but there are three types of QFP (2.0 mm ~ 3.6 mm thick), LQFP(1.4mm thick), and TQFP(1.0mm thick) according to the thickness of the package body. In addition, some LSI manufacturers refer to QFP with a pin center distance of 0.5mm as contraction QFP or SQFP and VQFP. However, some manufacturers call QFP with a pin center distance of 0.65mm and 0.4mm as SQFP, which makes the name a little confusing. The disadvantage of QFP is that when the center distance of pins is less than 0.65mm, pins are easy to bend. To prevent pin deformation, several improved QFP varieties have appeared. For example, BQFP (see BQFP) with tree finger cushions at four corners of the package; GQFP with resin protection ring covering the front end of pin (see Gqfp); TPQFP (see TPQFP) can be tested by setting test bumps in the package body and placing them in a special clamp to prevent pin deformation. In terms of logic LSI, many development products and high-reliability products are packaged in multilayer ceramic QFP. Products with a minimum pin pitch of 0.4mm and a maximum PIN of 348 have also been published. In addition, glass-sealed ceramic QFP is also used (see Gerqa d).

48. QFP(FP)(QFP fine pitch) QFP with small center distance. The name specified in the standard of Japan Electronic Machinery Industry Association. Guide the QFP with the foot center distance of 0.55mm, 0.4mm, 0.3mm, and less than 0.65mm (see QFP).

49. Another name for QIC(quad in-line ceramic package) ceramic QFP. Names adopted by some semiconductor manufacturers (see QFP and Cerquad).

50, QIP(quad in-line plastic package) Another name for plastic QFP. Names adopted by some semiconductor manufacturers (see QFP).

51. QTCP(quad tape carrier package) is packaged with four-sided pins. In one of TCP packages, pins are formed on the insulating tape and led out from four sides of the package. It is a thin package using TAB technology (see TAB, TCP).

52. QTP(quad tape carrier package) four-side lead with load package. The name was used by the Japan Electronic Machinery Industry Association for the outline specification of QTCP in April 1993 (see TCP).

53. Quil (quad in-line) Another name for QUIP (see Quip).

54. QUIP(quad in-line package)Four-pin in-line package. The pins are led out from the two sides of the package, and every other pin is staggered and bent down into four columns. The pin pitch is 1.27mm, and when inserted into the printed substrate, the insertion pitch becomes 2.5 mm. Therefore, it can be used for standard printed circuit boards. It is a smaller package than the standard DIP. Japan Electric Company has adopted some kinds of packages in the microcomputer chips of desktop computers and household appliances. There are two kinds of materials: ceramic and plastic. Number of pins 64.

55. SDIP (shrink dual in-line package) shrink DIP. One of the plug-in packages, has the same shape as DIP, but the pin center distance (1.778mm) is smaller than DIP(2.54 mm), so it is called this name. The number of pins is from 14 to 90. Also known as sh-dip. There are two kinds of materials: ceramic and plastic.

56. SH-DIP (shrink dual in-line package) is the same as SDIP. The name was adopted by some semiconductor manufacturers.

57. Another name for SIL(single in-line)SIP (see SIP). European semiconductor manufacturers mostly use the name SIL.

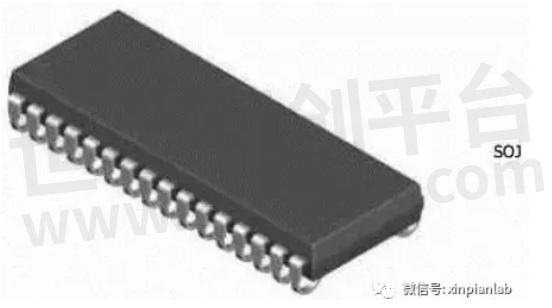

58. SIMM(single in-line memory module) single-column memory module. A memory module equipped with electrodes only near one side of the printed substrate. Usually refers to the component inserted into the socket. Standard SIMM has two specifications: 30 electrodes with a center distance of 2.54mm and 72 electrodes with a center distance of 1.27mm SIMM with 1 megabit DRAM and 4 megabit DRAM packaged by SOJ on one or both sides of printed substrate has been widely used in personal computers, workstations and other devices. At least 30 ~ 40% of DRAM is assembled in SIMM.

59. SIP(single in-line package) single in-line package. The pins are led out from one side of the package and arranged in a straight line. When assembled on a printed substrate, the package is side-standing. Pin-to-pin spacing is usually 2.54mm, and the number of pins ranges from 2 to 23, most of which are custom products. The shapes of packages are different. Some packages with the same shape as ZIP are also called SIP.

60. SK-DIP (Skinny dual in-line package) is a kind of DIP. Refers to a narrow DIP with a width of 7.62mm and a pin center distance of 2.54mm Commonly referred to as DIP (see DIP).

61. SL-DIP (Slim dual in-line package) is a kind of DIP. It refers to a narrow DIP with a width of 10.16mm and a pin center distance of 2.54mm Commonly referred to as DIP.

62、SMD(surface mount devices) surface mount devices. Occasionally, some semiconductor manufacturers classify SOP as SMD (see SOP).

63. Another name for SO(small out-line)SOP. Many semiconductor manufacturers in the world adopt this nickname. (see SOP).

64. SOI (Small Out-Line I-Led Package) I-shaped lead small outline package. One of the surface mount packages. The pins are led out from both sides of the package in an I-shape with a center-to-center distance of 1.27 mm. The mounting area is less than SOP. Hitachi adopted this package in analog IC (IC for motor drive). The argument is 26.

65. Another name for SOIC (small out-line integrated circuit) is SOP (see SOP). Many foreign semiconductor manufacturers have adopted this name.

66. SOJ (Small Out-Line J-Led Package) J-shaped pin small outline package. One of the surface mount packages. The pins lead out from both sides of the package in a J shape, hence the name. They are usually plastic products, mostly used in memory LSI circuits such as DRAM and SRAM, but most of them are DRAM. Many DRAM devices packaged with SO J are assembled on SIMM. The pin spacing is 1.27mm, and the PIN is from 20 to 40 (see SIMM).

Fig.12

67、SQL (Small Out-Line L-Led Package) is the name adopted for SOP according to the JEDEC (United States Joint Electronic Equipment Engineering Committee) standard (see SOP).

68. SOPF (Small Out-Line Non-Fin) SOP without heat sink. Same as the usual SOP. NF(non-fin) mark is intentionally added to show the difference of non-heatsink in the power IC package. Names adopted by some semiconductor manufacturers (see SOP).

69. SOF(small Out-Line package) Small Form Factor Package. In one of the surface mount packages, the leads are led out from both sides of the package in a gullwing shape (L-shaped). There are two kinds of materials: plastic and ceramic. Also known as SOL and DFP. SOP is not only used in memory LSI, but also widely used in circuits such as ASSP. SOP is the most popular surface mount package in the field where the input and output terminals do not exceed 10 ~ 40. The pin spacing is 1.27mm, and the number of pins ranges from 8 to 44. In addition, SOP with a pin center distance less than 1.27mm is also called SSOP;; SOP with an assembly height of less than 1.27mm is also called TSOP (see SSOP, TSOP). There is also an SOP with a heat sink.

70. SOW (Small Outline Package (Wide-JYPE)) wide-body SOP. The name was adopted by some semiconductor manufacturers. Summary of chip types: Is there one you use?

- +1 Like

- Add to Favorites

Recommend

- Dark tide in the shortage market: chip refurbishment

- The RS3005 Chip Developed by Runic Technology Helped The System MCU to Complete The Power Supply

- FTDI’s USB Interface Chips FT232R Can Be Integrated into Gaming Controller

- Linear Power Supply Chip HKT6206 Can Be Widely Used in Reference Voltage Sources, Cameras and Other Products

- Bringing WIFI RF Front-end Chips, Low-noise Amplifiers, 5G Small Base Station RF Chips, CHIPBETTER Announced a Distribution with Sekorm

- 6 Bluetooth Beacons Based on nrf51822/nRF52832/nRF52810 Chip Solutions

- XBLW Chip Bo Le Analog Chip Series: Signal Chain Chips (Part 4)

- Focusing on design of security ASIC chip, NEOWINE provides anti-copy encryption chip, data security encryption chip, etc.

This document is provided by Sekorm Platform for VIP exclusive service. The copyright is owned by Sekorm. Without authorization, any medias, websites or individual are not allowed to reprint. When authorizing the reprint, the link of www.sekorm.com must be indicated.