DDR5: How Faster Memory Speeds Shapes the Future?

Faster data processing requires faster memory. Double data rate synchronous dynamic random-access memory (DDR SDRAM) enables the world's computers to work with the data in memory. DDR is used everywhere — not just in servers, workstations, and desktops, but it is also embedded in consumer electronics, automobiles, and other system designs. DDR SRAM is used for running applications and doing computations at blazing speeds, and the DDR standard ensures that memory providers all follow the same level of quality and speed for reading and writing to memory.

Each new generation of the DDR standard, defined by the Joint Electronic Devices Engineering Council (JEDEC), delivers significant improvements over the previous generation including increased speeds, reduced footprint, and improved power efficiency. The latest standard, DDR5, was released in 2021. Developers are already eager to take advantage of the incredible data rates: up to 6.4 gigatransfers per second (GT/s), doubling that of the previous generation.

These memory speed improvements will enable technologies which rely heavily on near-instant data-processing. However, these improvements introduce new design and test challenges for memory designers and manufacturers. In this article, Keysight will disscuss how the DDR5 standard deals with these challenges, how developers are taking advantage of DDR5 in emerging technologies, and what the next generation of DDR might look like.

Faster, not wider

Since the origins of SDRAM, engineers have faced challenges with increasing memory speeds. They have found to find ways to write and read faster and more efficiently to speed up processing in their designs. DDR SDRAM became the standard in the late 1990s, and has since been improved upon many times over, usually doubling the bit rate with each generation.

Faster DDR bit rates are possible by transmitting the signal faster or more bits at a time. However, increasing the number of pins on a device above a certain amount is unrealistic and expensive. In fact, DDR5 has the same number of pins as DDR4. Faster signal speed alone is the method of choice to increase memory bit rates for next-generation devices.

With faster speed comes challenges

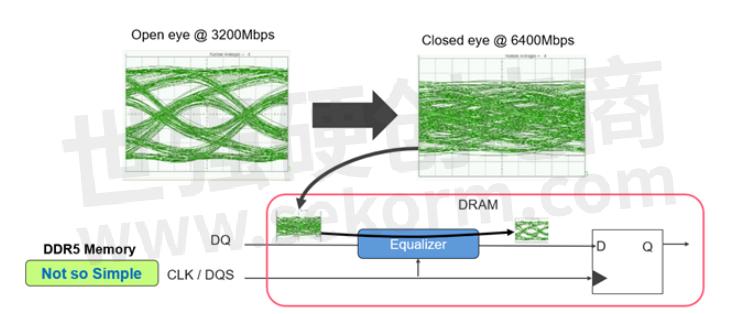

DRAM processes are inherently anti-speed since the bits are stored in charged capacitors. Capacitance can cause distortion in signals operating at high speed. This appears as a closed eye diagram on an oscilloscope, which closes more and more as the bit rate increases to its maximum bandwidth. The bits become indistinguishable at the highest rates, as shown in the closed eye in figure 1.

Figure 1: New to DDR5 is an equalizer on the data path to filter noise from high-speed transmission

To solve this problem, DDR5 requires equalization to filter out the noise, keeping the signal integrity high and reopening the eye. Unlike high-speed serial communication, DDR5 puts the equalization into a controller on the transmitter side, rather than in the receiver. This keeps all the logic out of the DRAM itself but adds a new element between the DIMM pins and the RAM chip, which was not present in DDR4. All of this culminates in a more sophisticated, faster memory transfer system to reach 6GT/s while maintaining a low bit error rate.

Faster memory enables the future

DDR5 is still in the early phases of adoption. JEDEC released the standard in July 2021. The first CPU platform to support DDR5 was released in early 2022. However, this platform still includes DDR4 support, so it could be some time before the industry accepts DDR5 as the de-facto memory standard. Over the next couple of years, more personal computers, servers, and embedded systems will take advantage of the higher speed, lower power, and greater memory capacity available with DDR5.

Internet-of-Things (IoT) and Vehicle-to-Everything (V2X) autonomous vehicles are just two of the many technologies being enabled by 5G which will interconnect billions of devices to cloud services. The data storage infrastructure required to process all that data sent to the cloud will need quicker and more efficient memory than anything we've seen yet, especially in time- and safety-critical applications like V2X. DDR5 is a huge step, alongside faster wireless communication, to enable these new technologies. But as these use cases become reality, will DDR5 be fast enough?

DDR6: Doubling the data rate of DDR5

DDR5 is just starting to be adopted into the market, but JEDEC and early-adopters are already looking forward to the next generation. DDR6 is likely to double the maximum bit rate of its predecessor, as all previous DDR generations have done. One memory manufacturer announced in late 2021 that they have begun development of DDR6 with JEDEC, and that the standard could hit speeds of greater than 12GT/s and quadruple the memory capacity. But considering the speed challenges discussed previously, reaching 12GT/s requires new innovations to successfully transmit the signal faster with causing distortion.

One possibility is for DDR6 to take after other standards such as Wi-Fi by using pulse amplitude modulation (PAM) or quadrature amplitude modulation (QAM) signaling. DDR5 already opened the door for adding complex signaling to the standard, so it makes sense that these methods may be used to increase the bit rate further in the future.

The New Reality

Until DDR6 becomes a reality, developers are still trying to make the move from DDR4 to the new DDR5 standard. The slightly more complicated nature of the DDR5 standard means that simulation, validation, and compliance tests become trickier to perform and margins for error are even smaller. Keysight is heavily engaged with JEDEC and early adoption partners of the DDR5 standard.

- +1 Like

- Add to Favorites

Recommend

- Alliance Memory Developed Low-Power, High-Speed Mobile CMOS DDR SDRAMs With 256-Mb, 512-Mb, 1-Gb, and 2-Gb Densities

- Alliance Memory Introduced High-Speed CMOS DDR SDRAMs With 64, 128, 256, and 512Mb Densities and Temperature Range From -40℃ to +85℃

- Alliance Memory Introduced 1Gb High-Speed CMOS DDR SDRAM AS4C128M8D1-6TIN in 128M x 8 Configuration

- Alliance Memory Introduced High-Speed CMOS DDR SDRAMs With 256Mb, 512Mb, and 1Gb Densities in 60-Ball TFBGA and 66-Pin TSOP II Packages

- New 8Gb LPDDR4X SDRAM, On-chip ECC and AEC-Q100 Qualified

- 3A Sink and Source DDR Termination Regulator Supporting 2.5V, 3.3V and 5V Power Rails

- Alliance Memory Launched 256Mb High-Speed CMOS SDRAMs in the 54-Pin TSOP II Package

- A Brief Introduction of DDR4 SDRAMs, LPDDR4x SDRAMs and eMMC Components of ALLIANCE

This document is provided by Sekorm Platform for VIP exclusive service. The copyright is owned by Sekorm. Without authorization, any medias, websites or individual are not allowed to reprint. When authorizing the reprint, the link of www.sekorm.com must be indicated.