How to Build AMI Models for DDR5 Memory Interfaces

Traditionally, double data rate (DDR) technologies have relied on timing measurements, such as setup and hold times. As the standard evolves and the transfer rate increases, signal integrity becomes a lot more challenging.

For DDR5, timing measurements have been replaced with eye mask measurements for both data and command address signals. SPICE transient simulators are no longer the right approach for the latest DDR5 and LPDDR5 memory standards.

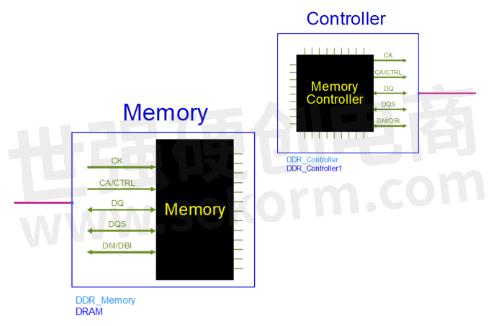

The new standards add equalization (EQ) on both the memory controller and the DRAM, and traditional simulation tools can't model at that complexity.

Figure 1. DDR5 standards add equalization (EQ) on both the memory controller and the DRAM.

Input/Output Buffer Information Specification (IBIS) Algorithmic Modeling Interface (AMI) – or IBIS-AMI – models support statistical and time-domain channel simulations and represent the processing behavior inside the chip accurately and efficiently. However, access to models can be a bottleneck for new design work.

To create fast and accurate models that can predict eye closure, here are three ways that an AMI model builder can help you with your DDR5 and LPDDR5 modeling.

1. Generate Models Based on Industry Standards

Advanced AMI model builder software helps you create a new AMI model or edit a pre-existing model using an intuitive, wizard-style interface built to meet JEDEC specifications for DDR5 and LPDDR5. This allows you to select the modeling options you need.

Figure 2. AMI model builder software with an intuitive, wizard-style interface built to meet JEDEC specifications for DDR5.

2. Predict Eye-Opening with Confidence

To ensure the signal's eye opens up, it is crucial that you apply the proper equalization. This includes finding the optimum decision feedback equalization (DFE) taps for your receiver equalization.

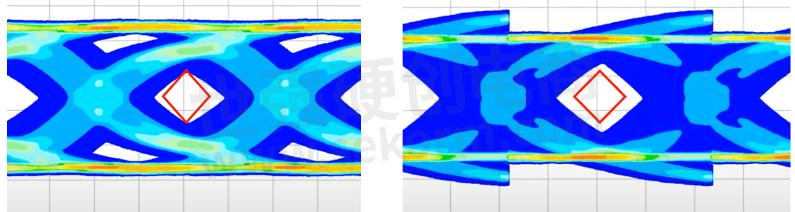

Figure 3. IBIS-AMI models with forwarded clocking capabilities better predict eye-opening measurement with simulation.

At DDR5 speeds, the data eye is expected to close. AMI model builder software can generate AMI models with forwarded clocking. This means it takes in both data and data strobe waveforms as input to the model.

This advanced modeling capability ensures that your simulations will handle both jitter tracking and skew adjustment, also known as unmatched IO.

3. Streamline Your AMI Workflow

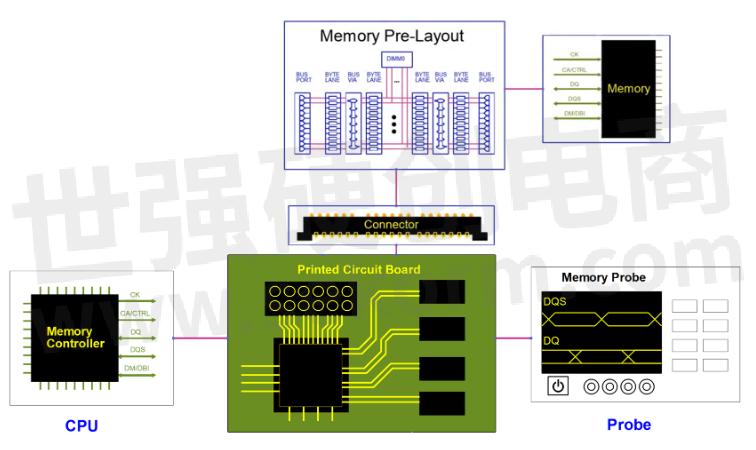

Once you've completed setting up your IBIS-AMI model, you're now ready to send off your files. If you're using PathWave ADS Memory Designer, the AMI builder quickly generates 4 file types: .ami, .dll, .cfg., and .ibs, making the models easy to consume and use in your simulations.

Figure 4. PathWave ADS Memory Designer layout with the memory controller and DRAM.

If you are a memory system engineer or a silicon modeling engineer, you can quickly and easily generate IBIS-AMI models using the latest version of PathWave ADS.

- +1 Like

- Add to Favorites

Recommend

- Keysight Introduces PathWave ADS 2024 to Accelerate 5G mmWave Design and Pioneer 6G Development

- Keysight PathWave Software Selected by Menlo Micro to Reduce Design Cycle for New Radio Frequency Microelectromechanical Switch

- Keysight PathWave System Design 2023 Software Accelerates RF System Design and Digital Mission Engineering Workflows for 5G Non-Terrestrial Networks

- Keysight Introduces PathWave Design 2024 with Automation and Collaboration Support for Enterprise EDA Workflows

- Keysight Launches New Design and Simulation Software for Radio Frequency and Microwave Designers

- Keysight Unveils Comprehensive Design and Test Workflow for Next-Generation Memory Designs

- 5 Quick Tips You Should Know as a New PathWave BenchVue User

- Boosting Your Manufacturing Analytics System with Keysight’s Pathwave Manufacturing Analytics (PMA)

This document is provided by Sekorm Platform for VIP exclusive service. The copyright is owned by Sekorm. Without authorization, any medias, websites or individual are not allowed to reprint. When authorizing the reprint, the link of www.sekorm.com must be indicated.